Integrated circuits

Supplement to Book IC 11 N

1986

Linear LSI

Signetics

**Elcoma** – Philips Electronic Components and Materials Division – embraces a world-wide group of companies operating under the following names:

IBRAPE

Miniwatt

Signetics

Mullard

PHILIPS

Elcoma offers you a technological partnership in developing your systems to the full. A partnership to which we can bring

- world-wide production and marketing

- know-how

- systems approach

- continuity

- broad product line

- fundamental research

- leading technologies

- applications support

- quality

## LINEAR LSI

|                                                              |                                         | page |

|--------------------------------------------------------------|-----------------------------------------|------|

| Preface                                                      |                                         | ix   |

| Product status definitions                                   |                                         | x    |

| Contents                                                     |                                         | xi   |

|                                                              |                                         |      |

| Section 1 — Selection guide                                  |                                         |      |

| Index                                                        |                                         |      |

| SO package availability                                      |                                         |      |

| Ordering information                                         | • • • • • • • • • • • • • • • • • • • • | 1-5  |

| Section 2 — Quality and Reliability                          |                                         |      |

| Quality and Reliability                                      |                                         | 2.3  |

| Quanty and Renability                                        | · · · · · · · · · · · · · · · · · · ·   | 2-3  |

| Section 3 — Military                                         |                                         |      |

| Index                                                        |                                         | 3-1  |

| Military Errata                                              |                                         | 3-3  |

|                                                              |                                         |      |

| Section 4 — Interface/data conversion products               |                                         |      |

| Index                                                        | •••••                                   | 4-1  |

| Section 5 — Communication                                    |                                         |      |

| Index                                                        |                                         | 5-1  |

| Section 6 — Amplifiers                                       |                                         |      |

| Index                                                        |                                         | 6-1  |

|                                                              |                                         |      |

| Section 7 — Professional analogue ICs                        |                                         |      |

| Index                                                        |                                         | 7-1  |

|                                                              |                                         |      |

| Section 8 — Applications                                     |                                         |      |

| Index                                                        | • • • • • • • • • • • • • • • • • • • • | 8-1  |

| Section 9 — Package outlines                                 |                                         |      |

| Index                                                        |                                         | 0.1  |

|                                                              | • • • • • • • • • • • • • • • • • • • • | 9-1  |

| Section 10 — Forthcoming new products and alphanumeric index |                                         |      |

| Index                                                        | • • • • • • • • • • • • •               | 10-1 |

| Forthcoming new products                                     |                                         |      |

| Alphanumeric index                                           |                                         |      |

### DATA HANDBOOK SYSTEM

Our Data Handbook System comprises more than 60 books with specifications on electronic components, subassemblies and materials. It is made up of four series of handbooks:

**ELECTRON TUBES**

BLUE

**SEMICONDUCTORS**

RED

INTEGRATED CIRCUITS

**PURPLE**

#### COMPONENTS AND MATERIALS

**GREEN**

The contents of each series are listed on pages iv to viii.

The data handbooks contain all pertinent data available at the time of publication, and each is revised and reissued periodically.

When ratings or specifications differ from those published in the preceding edition they are indicated with arrows in the page margin. Where application information is given it is advisory and does not form part of the product specification.

Condensed data on the preferred products of Philips Electronic Components and Materials Division is given in our Preferred Type Range catalogue (issued annually).

Information on current Data Handbooks and on how to obtain a subscription for future issues is available from any of the Organizations listed on the back cover.

Product specialists are at your service and enquiries will be answered promptly.

## ELECTRON TUBES (BLUE SERIES)

The blue series of data handbooks comprises:

| T1  | Tubes for r.f. heating                                                                                                           |

|-----|----------------------------------------------------------------------------------------------------------------------------------|

| T2a | Transmitting tubes for communications, glass types                                                                               |

| T2b | Transmitting tubes for communications, ceramic types                                                                             |

| Т3  | Klystrons                                                                                                                        |

| Т4  | Magnetrons for microwave heating                                                                                                 |

| Т5  | Cathode-ray tubes Instrument tubes, monitor and display tubes, C.R. tubes for special applications                               |

| Т6  | Geiger-Müller tubes                                                                                                              |

| Т8  | Colour display systems Colour TV picture tubes, colour data graphic display tube assemblies, deflection units                    |

| Т9  | Photo and electron multipliers                                                                                                   |

| Г10 | Plumbicon camera tubes and accessories                                                                                           |

| Г11 | Microwave semiconductors and components                                                                                          |

| Γ12 | Vidicon and Newvicon camera tubes                                                                                                |

| Г13 | Image intensifiers and infrared detectors                                                                                        |

| Г15 | Dry reed switches                                                                                                                |

| Г16 | Monochrome tubes and deflection units  Black and white TV picture tubes, monochrome data graphic display tubes, deflection units |

## SEMICONDUCTORS (RED SERIES)

The red series of data handbooks comprises:

| S1        | $\label{eq:continuous} \textbf{Diodes} \\ \textbf{Small-signal silicon diodes, voltage regulator diodes ($<$1,5$ W), voltage reference diodes, tuner diodes, rectifier diodes} \\$ |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S2a       | Power diodes                                                                                                                                                                       |

| S2b       | Thyristors and triacs                                                                                                                                                              |

| <b>S3</b> | Small-signal transistors                                                                                                                                                           |

| S4a       | Low-frequency power transistors and hybrid modules                                                                                                                                 |

| S4b       | High-voltage and switching power transistors                                                                                                                                       |

| S5        | Field-effect transistors                                                                                                                                                           |

| S6        | R.F. power transistors and modules                                                                                                                                                 |

| <b>S7</b> | Surface mounted semiconductors                                                                                                                                                     |

| S8a       | Light-emitting diodes                                                                                                                                                              |

| S8b       | Devices for optoelectronics Optocouplers, photosensitive diodes and transistors, infrared light-emitting diodes and infrared sensitive devices, laser and fibre-optic components   |

| <b>S9</b> | Power MOS transistors                                                                                                                                                              |

| S10       | Wideband transistors and wideband hybrid IC modules                                                                                                                                |

| S11       | Microwave transistors                                                                                                                                                              |

| S12       | Surface acoustic wave devices                                                                                                                                                      |

| S13       | Semiconductor sensors                                                                                                                                                              |

## INTEGRATED CIRCUITS (PURPLE SERIES)

The purple series of data handbooks comprises:

| EXISTI | NG SERIES                                                                                   | Superseded by:                |

|--------|---------------------------------------------------------------------------------------------|-------------------------------|

| IC1    | Bipolar ICs for radio and audio equipment                                                   | IC01N                         |

| IC2    | Bipolar ICs for video equipment                                                             | IC02Na and IC02Nb             |

| IC3    | ICs for digital systems in radio, audio and video equipment                                 | IC01N, IC02Na and IC02Nb      |

| IC4    | Digital integrated circuits CMOS HE4000B family                                             |                               |

| IC5    | Digital integrated circuits — ECL<br>ECL10 000 (GX family), ECL100 000 (HX family), dedicat | IC08N red designs             |

| IC6    | Professional analogue integrated circuits                                                   | IC03N and Supplement to IC11N |

| IC7    | Signetics bipolar memories                                                                  |                               |

| IC8    | Signetics analogue circuits                                                                 | IC11N                         |

| IC9    | Signetics TTL logic                                                                         | IC09N and IC15N               |

| IC10   | Signetics Integrated Fuse Logic (IFL)                                                       | IC13N                         |

| IC11   | Microprocessors, microcomputers and peripheral circuitry                                    | IC14N                         |

March 1986 vi

| NEW SERIES          |                                                                             |                  |

|---------------------|-----------------------------------------------------------------------------|------------------|

| IC01N               | Radio, audio and associated systems Bipolar, MOS                            | (published 1985) |

| IC02Na              | Video and associated systems<br>Bipolar, MOS<br>Types MAB8031AH to TDA1524A | (published 1985) |

| IC02Nb              | Video and associated systems<br>Bipolar, MOS<br>Types TDA2501 to TEA1002    | (published 1985) |

| IC03N               | Integrated circuits for telephony                                           | (published 1985) |

| ICO4N               | HE4000B logic family<br>CMOS                                                |                  |

| IC05N               | HE4000B logic family — incased ICs<br>CMOS                                  | (published 1984) |

| IC06N*              | High-speed CMOS; PC74HC/HCT/HCU Logic family                                | (published 1986) |

| IC07N               | High-speed CMOS; PC54/74HC/HCT/HCU — uncased ICs Logic family               |                  |

| IC08N               | ECL 10K and 100K logic families                                             | (published 1984) |

| IC09N               | TTL logic series                                                            | (published 1984) |

| IC10N               | Memories<br>MOS, TTL, ECL                                                   |                  |

| IC11N               | Linear LSI                                                                  | (published 1985) |

| Supplement to IC11N | Linear LSI                                                                  | (published 1986) |

| IC12N               | Semi-custom gate arrays & cell libraries ISL, ECL, CMOS                     |                  |

| IC13N               | Semi-custom Integrated Fuse Logic                                           | (published 1985) |

| IC14N               | Microprocessors, microcontrollers & peripherals Bipolar, MOS                | (published 1985) |

#### Note

IC15N

Books available in the new series are shown with their date of publication.

**FAST TTL logic series**

vii March 1986

(published 1984)

<sup>\*</sup> Supersedes the IC06N 1985 edition and the Supplement to IC06N issued Autumn 1985.

## COMPONENTS AND MATERIALS (GREEN SERIES)

The green series of data handbooks comprises:

| C1         | Programmable controller modules PLC modules, PC20 modules                                   |

|------------|---------------------------------------------------------------------------------------------|

| C2         | Television tuners, coaxial aerial input assemblies, surface acoustic wave filters           |

| C3         | Loudspeakers                                                                                |

| C4         | Ferroxcube potcores, square cores and cross cores                                           |

| C5         | Ferroxcube for power, audio/video and accelerators                                          |

| C6         | Synchronous motors and gearboxes                                                            |

| <b>C</b> 7 | Variable capacitors                                                                         |

| C8         | Variable mains transformers                                                                 |

| C9         | Piezoelectric quartz devices                                                                |

| C10        | Connectors                                                                                  |

| C11        | Varistors, thermistors and sensors                                                          |

| C12        | Potentiometers, encoders and switches                                                       |

| C13        | Fixed resistors                                                                             |

| C14        | Electrolytic and solid capacitors                                                           |

| C15        | Ceramic capacitors                                                                          |

| C16        | Permanent magnet materials                                                                  |

| C17        | Stepping motors and associated electronics                                                  |

| C18        | Direct current motors                                                                       |

| C19        | Piezoelectric ceramics                                                                      |

| C20        | Wire-wound components for TVs and monitors                                                  |

| C21*       | Assemblies for industrial use HNIL FZ/30 series, NORbits 60-, 61-, 90-series, input devices |

| C22        | Film capacitors                                                                             |

<sup>\*</sup> To be issued shortly.

#### **PREFACE**

The linear LSI Division, one of five Signetics divisions, is a major supplier of a broad line of linear integrated circuits ranging from high-performance designs to many of the more popular industry standard devices and custom designs.

Employing Signatics' high quality processing and screening standards, the Linear LSI Division is dedicated to providing high quality Linear products to our worldwide customers. Our full product line addresses the needs of the EDP, Automotive, Industrial, Consumer and Communication markets.

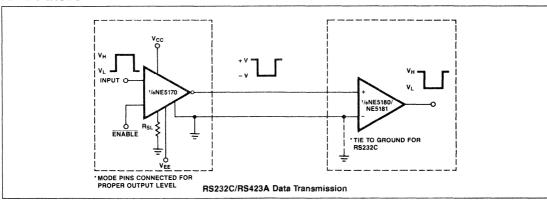

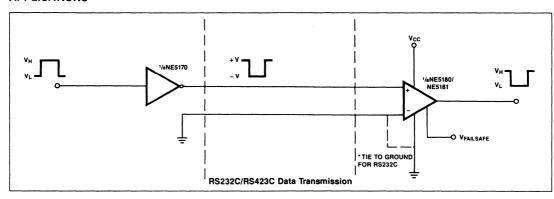

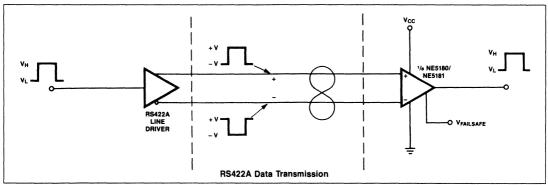

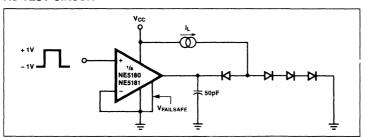

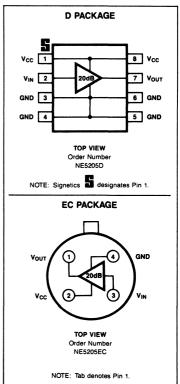

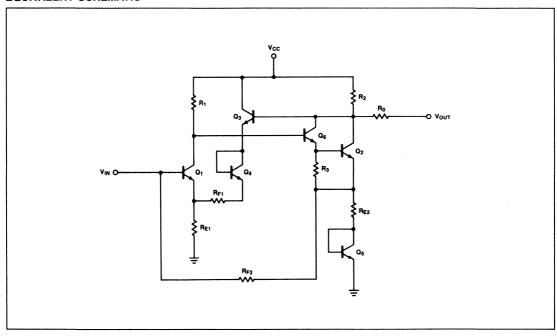

The 1986 Supplement to our Linear LSI book of 1985 provides complete technical data on our full line of interface, communication, amplifier, power conversion and control products. Among these you will find new entrants such as the NE5205 high frequency amplifier, NE5170 and NE5180/5181 octal line driver and receivers, and the DAC800 12-bit D/A Converter.

An applications section, selector guides and cross reference guides are also included in this volume,

Although every attempt has been made to insure accuracy of information in this manual, Signetics assumes no liability for inadvertent errors.

Signetics Linear LSI Marketing

## **PRODUCT STATUS DEFINITIONS**

| DEFINITION OF TERMS       |                            |                                                                                                                                                                                                                                                   |  |  |

|---------------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Data Sheet Identification | Product Status             | Definition                                                                                                                                                                                                                                        |  |  |

| Preview                   | Formative or In Design     | This data sheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                                                               |  |  |

| Advance Information       | Sampling or Pre-Production | This data sheet contains advance information and specifications are subject to change without notice.                                                                                                                                             |  |  |

| Preliminary               | First Production           | This data sheet contains preliminary data and supplementary data will be published at a later date<br>Signetics reserves the right to make changes at any time without notice in order to improve design and<br>supply the best possible product. |  |  |

| Product Specification     | Full Production            | This data sheet contains final specifications. Signetics reserves the right to make changes at any time without notice in order to improve design and supply the best possible product.                                                           |  |  |

## **CONTENTS**

| SECTION 1 — SELECTION G               | UIDE                                                                            |

|---------------------------------------|---------------------------------------------------------------------------------|

| By Part number                        |                                                                                 |

| By Part Number                        | 8-<br>8-<br>8-                                                                  |

| SO Package Availability               |                                                                                 |

| Ordering Information                  | 18                                                                              |

| SECTION 2 - QUALITY AN                | D RELIABILITY                                                                   |

| Quality and Reliability               | 2-:                                                                             |

| SECTION 3 - MILITARY                  |                                                                                 |

| Military Errata                       | 3-:                                                                             |

| SECTION 4 - INTERFACE/                | DATA CONVERSION PRODUCTS                                                        |

| - •                                   | 4-                                                                              |

|                                       | 4                                                                               |

| Symbols and definitions               | 4-                                                                              |

| Analog to Digital Converted SE/NE5030 | rs<br>10-bit High Speed Microprocessor-Compatible Analog to Digital Converter4- |

| Digital to Analog Converte            | rs                                                                              |

| DAC800                                | 12-bit D/A Converter                                                            |

| SE/NE5018                             | 8-bit Microprocessor-Compatible D/A Converter                                   |

| SE/NE5019                             | 8-bit Microprocessor-Compatible D/A Converter                                   |

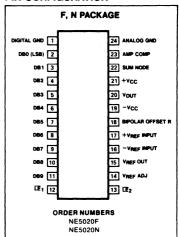

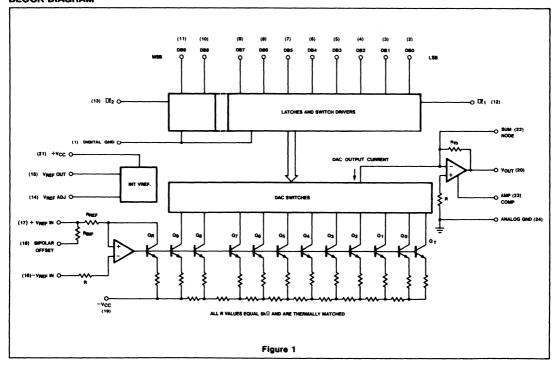

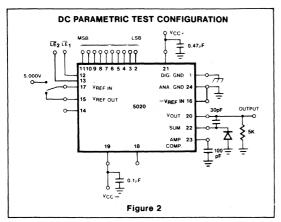

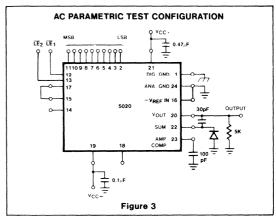

| SE/NE5020<br>NE5150/NE5151            | 10-bit Microprocessor-Compatible D/A Converter                                  |

| Comparators                           | 4-4                                                                             |

| Drivers                               |                                                                                 |

|                                       | s                                                                               |

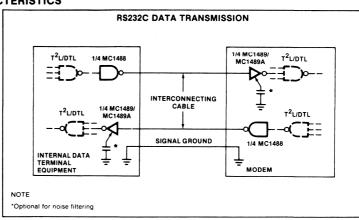

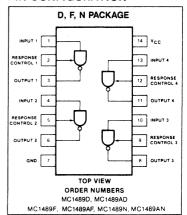

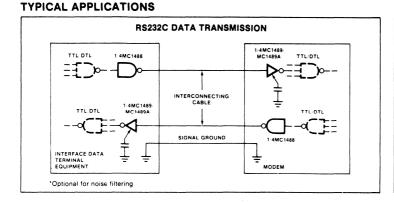

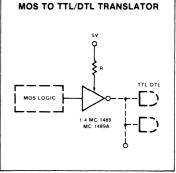

| MC1488                                | Quad Line Driver                                                                |

| MC1489/MC1489A                        | Quad Line Receivers                                                             |

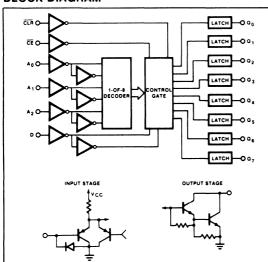

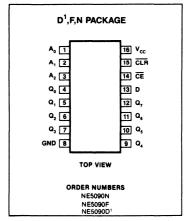

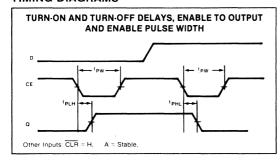

| NE5090                                | Addressable Relay Driver                                                        |

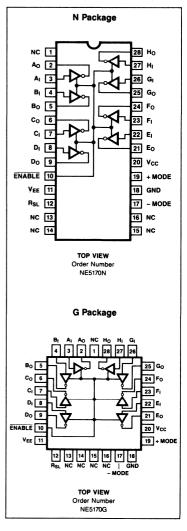

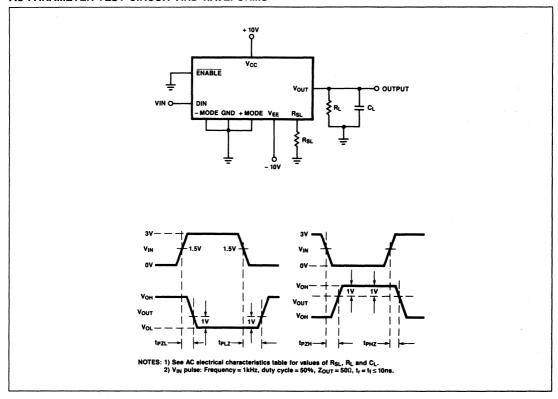

| NE5170                                | Octal Line driver                                                               |

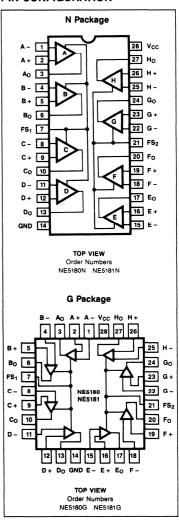

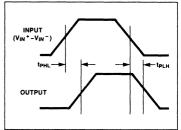

| NE5180/NE5181                         | Octal Line Receivers                                                            |

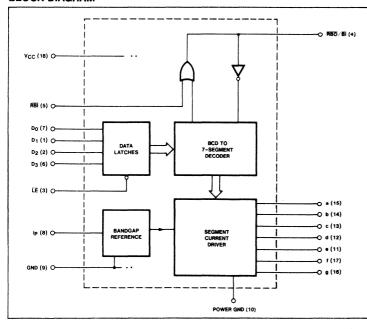

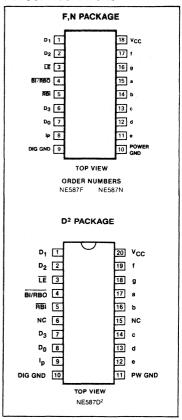

| NE587                                 | LED Decoder/Driver                                                              |

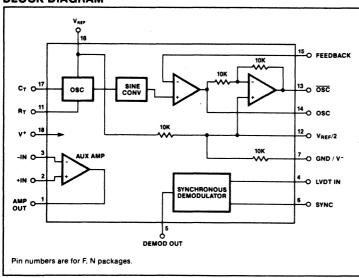

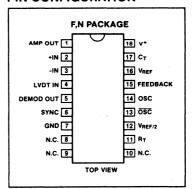

| Position Measurement<br>SE/NE5521     | LVDT Signal Conditioner                                                         |

| SECTION 5 — COMMUNICAT                | TION                                                                            |

| Index                                 | ······ 5-1                                                                      |

| Audio/Stereo                          | •                                                                               |

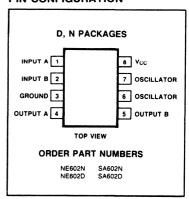

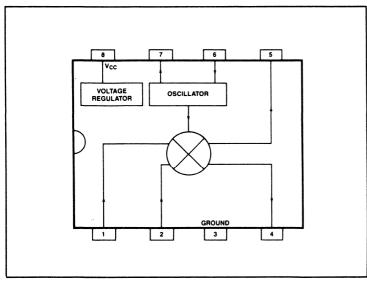

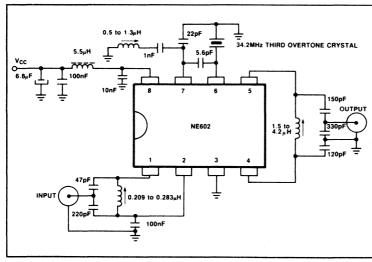

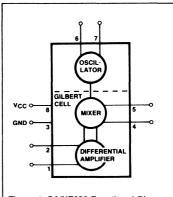

| SA/NE602                              | Double Balanced Mixer and Oscillator                                            |

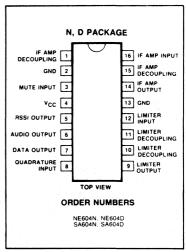

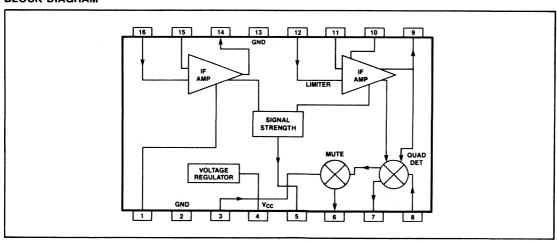

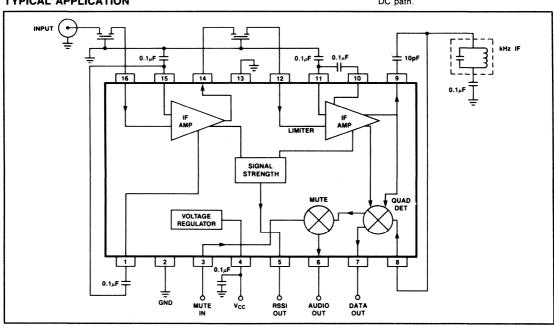

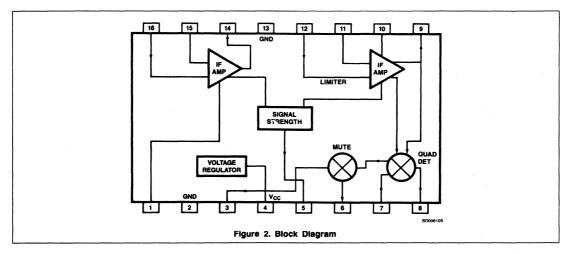

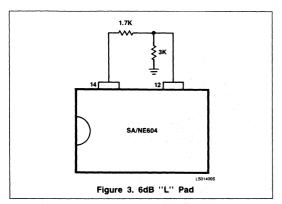

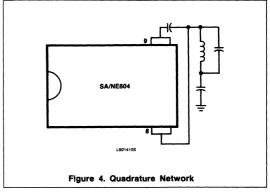

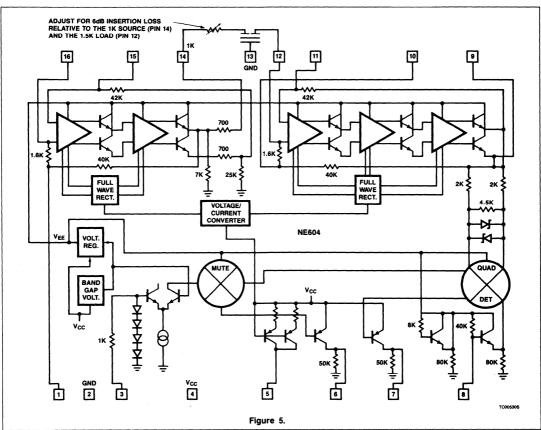

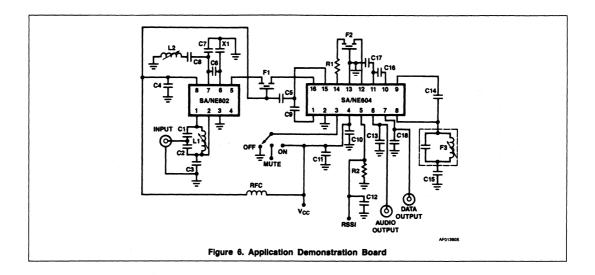

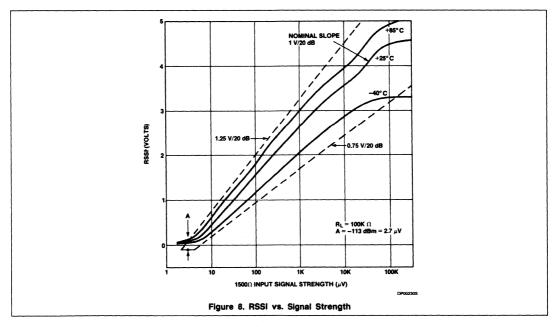

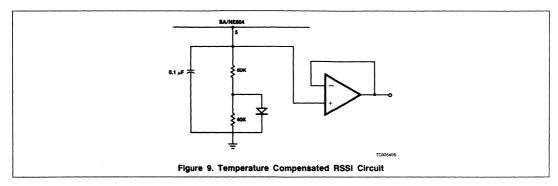

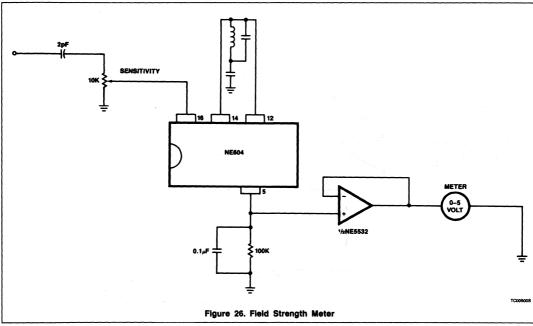

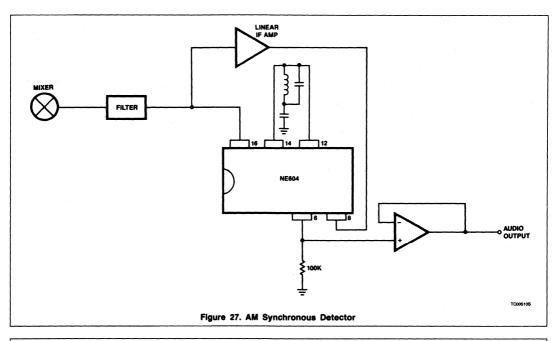

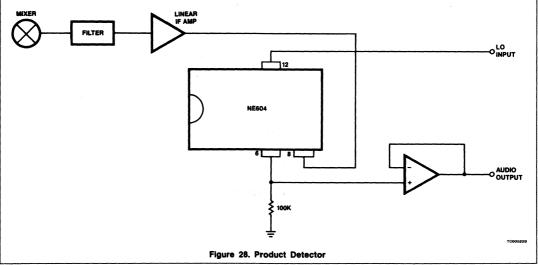

| SA/NE604                              | Low Power FM I.F. System                                                        |

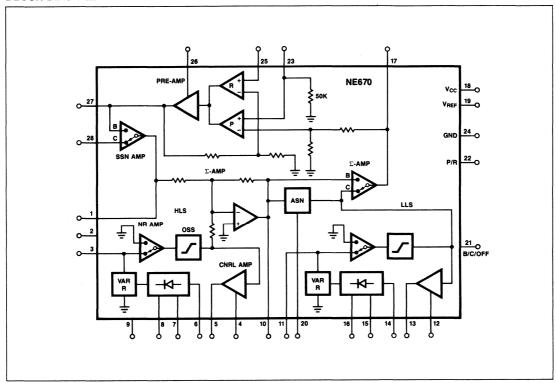

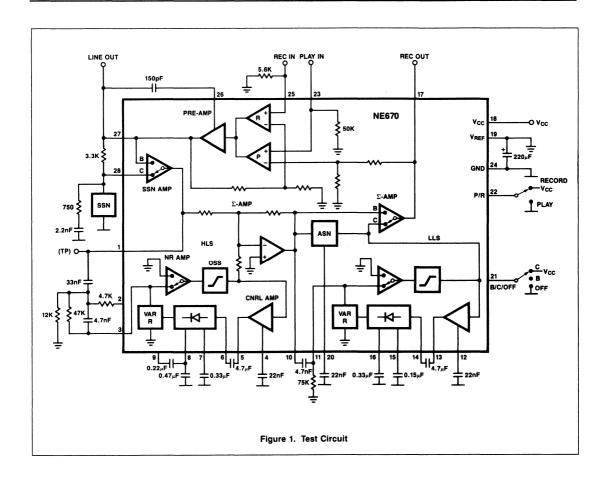

| NE670                                 | Low Voltage Dolby B/C Type IC                                                   |

| FM Radio                              |                                                                                 |

| SA/NE602                              | Double Balanced Mixer and Oscillator                                            |

| SA/NE604                              | Low Power FM I.F. System                                                        |

<sup>\*</sup> For up-to-date cross reference information contact your local sales office.

## **CONTENTS**

| SECTION 6 - AMP  | LIFIERS    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Index            |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Video<br>NE5205  |            | Wideband High Frequency Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SECTION 7 - PRO  | FESSION    | AL ANALOGUE ICs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Index            |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

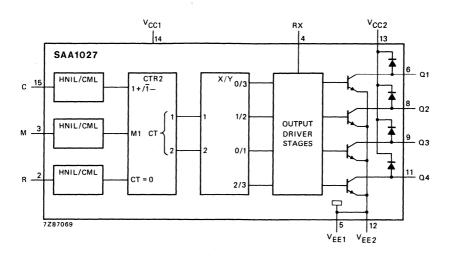

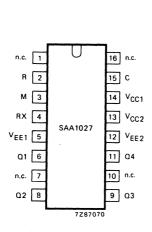

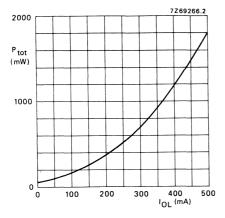

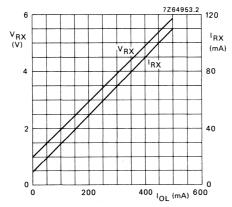

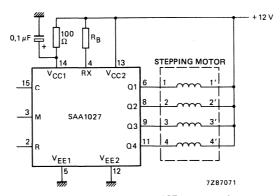

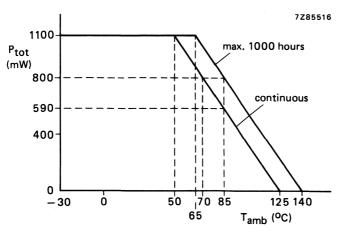

| SAA1027          |            | Stepping Motor Drive Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

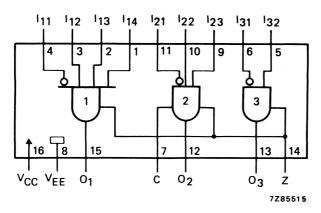

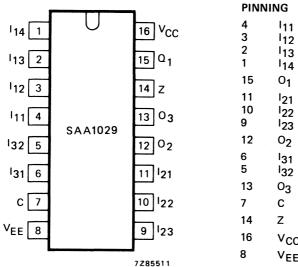

| SAA1029          |            | Universal Industrial Logic and Interface Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

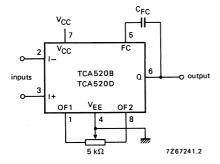

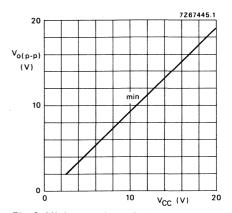

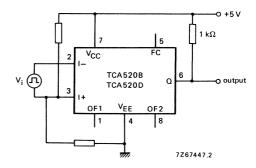

| TCA520B; D       |            | Operational Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

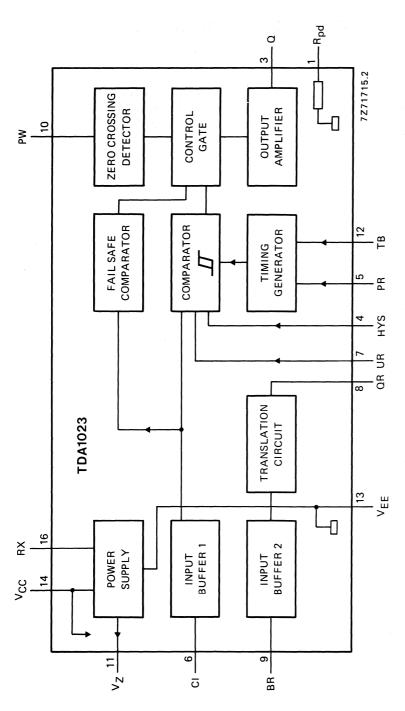

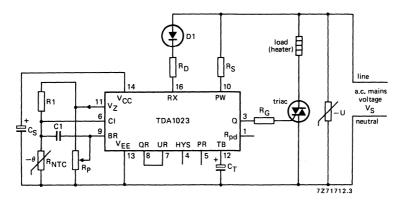

| TDA1023          |            | Proportional-Control Triac Triggering Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

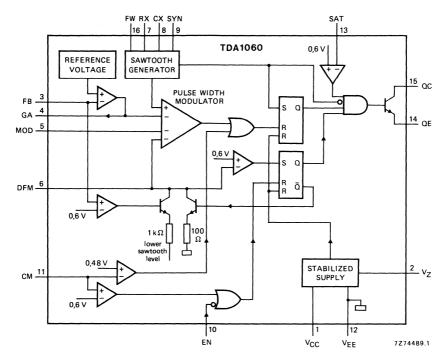

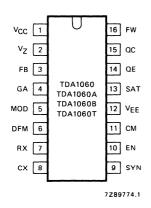

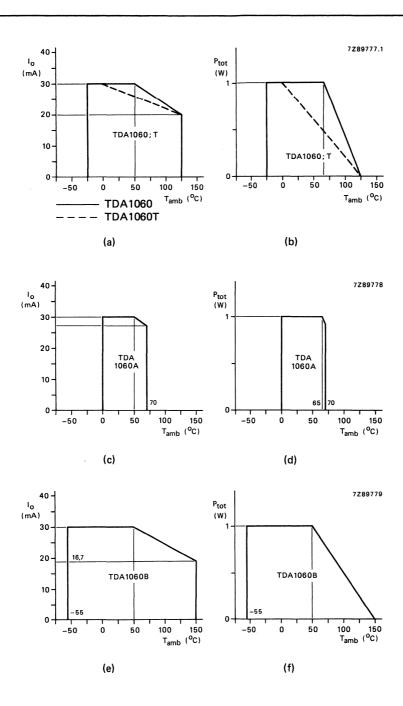

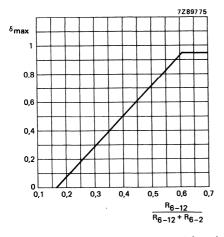

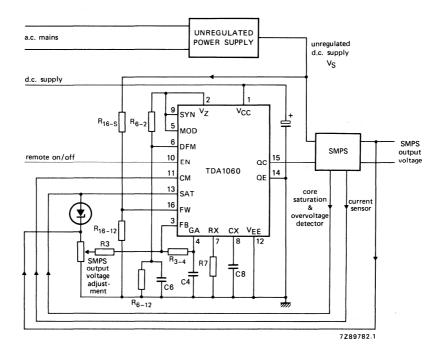

| TDA1060; A;      | ; B; T     | Control Circuit for SMPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| TDB1080; T       |            | I.F. Limiting Amplifier, FM Detector & Audio Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| TEA1017          |            | 13-Bit Series-Parallel Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

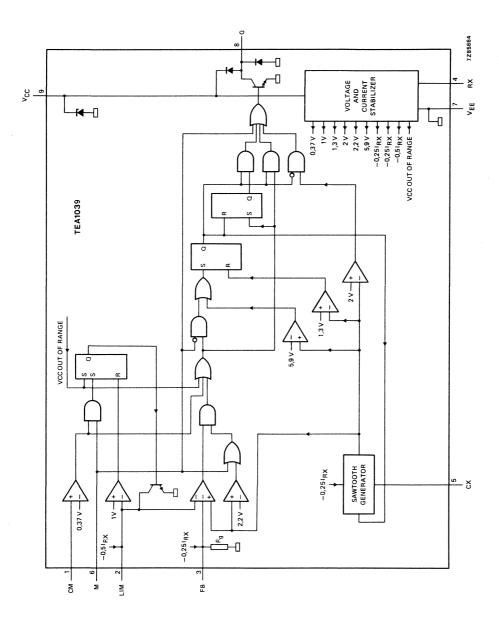

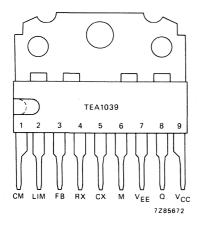

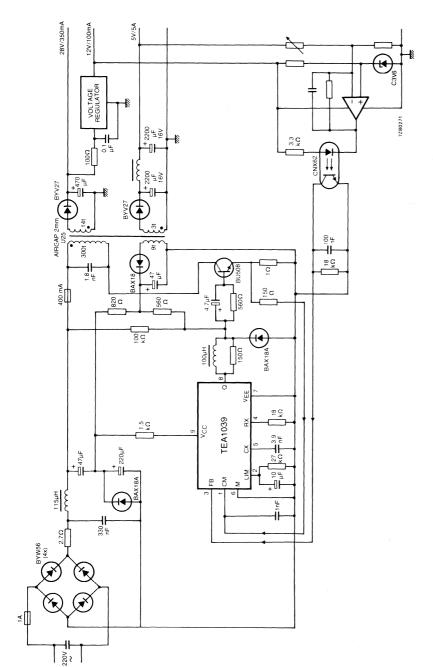

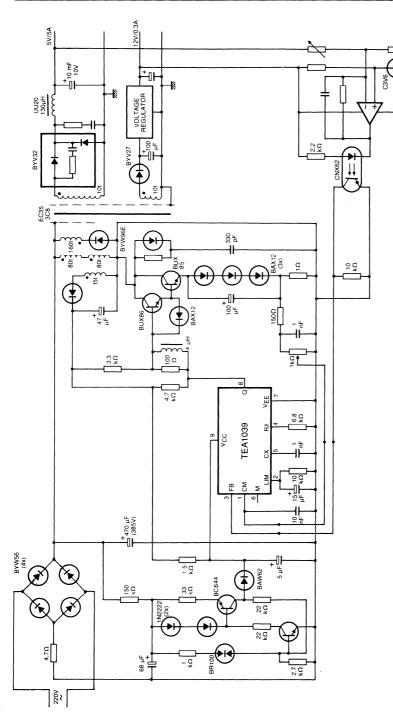

| TEA1039          |            | Control Circuit for SMPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SECTION 8 - APP  | LICATION   | NS CONTRACTOR OF THE CONTRACTO |

| Index            |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                  | es by Majo | r Product Category Communications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Audio            |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

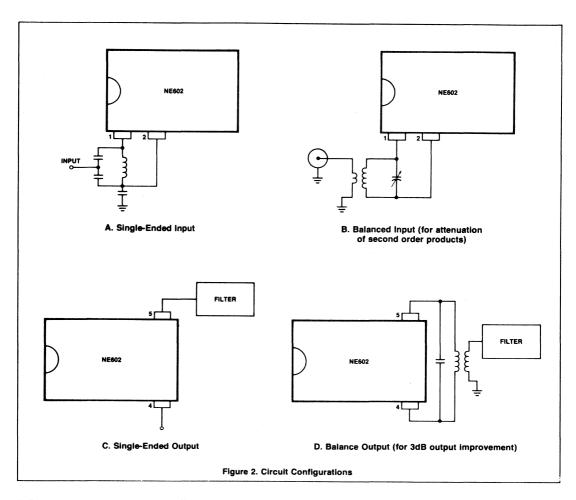

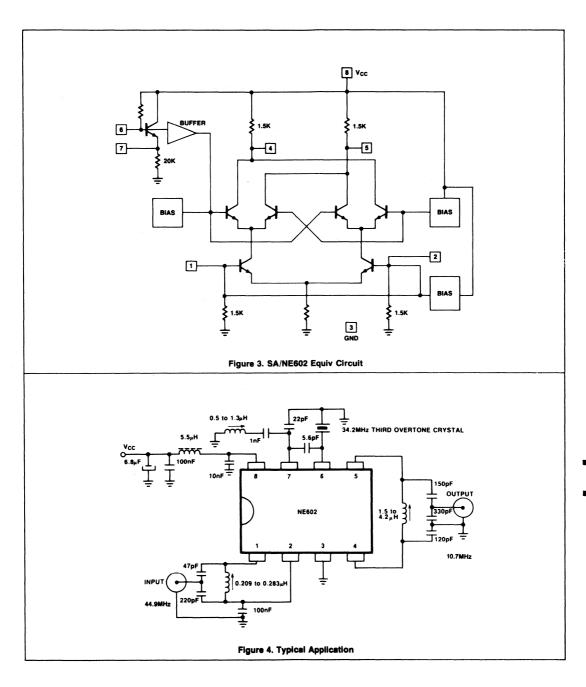

| AN198            |            | Designing with the SA/NE602                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| AN199            |            | Designing with the SA/NE604                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Amplifiers       |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Video Amplifiers |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

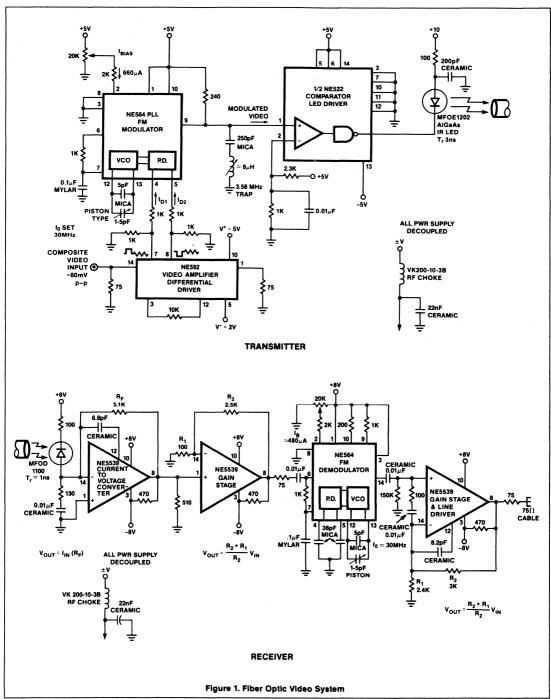

| AN146            |            | Wideband FM Composite Video Fiber Optic Link                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Power Conversio  |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

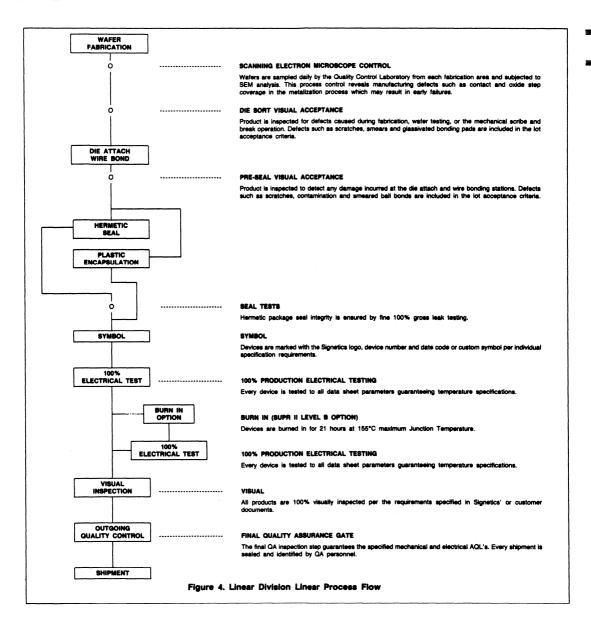

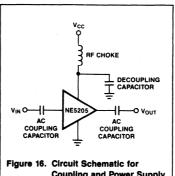

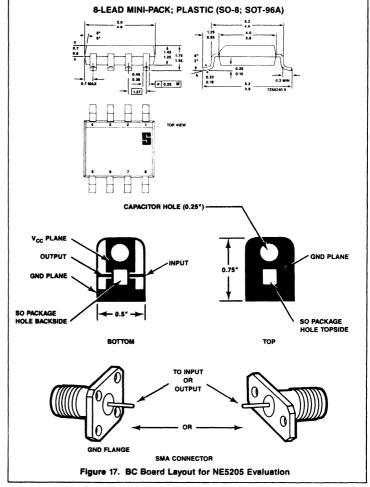

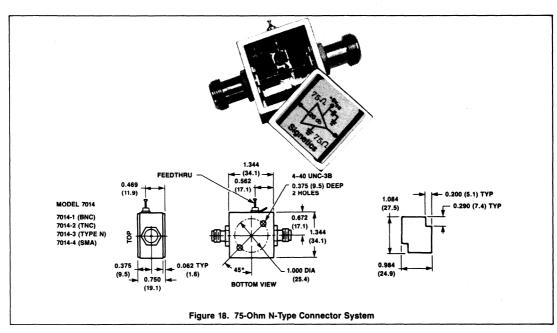

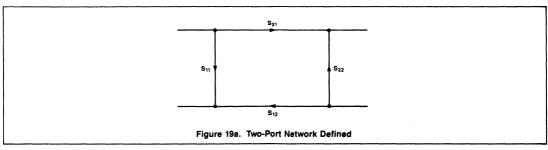

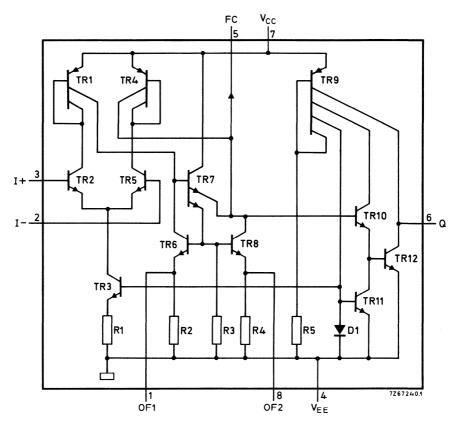

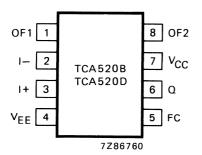

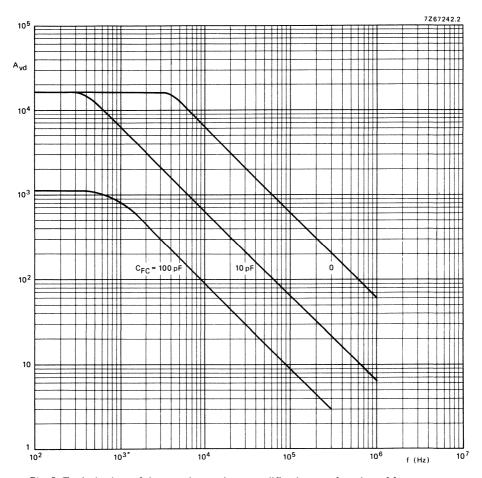

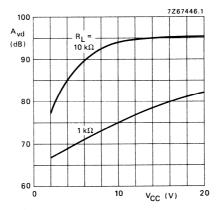

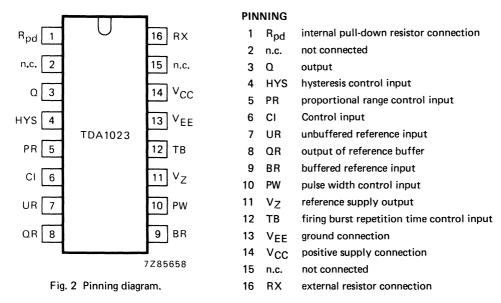

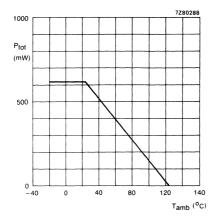

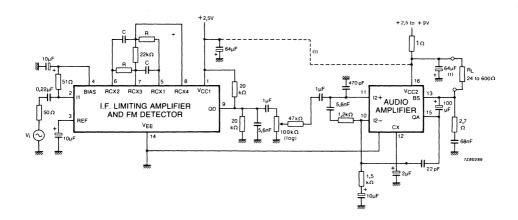

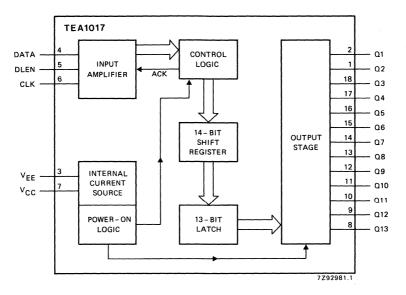

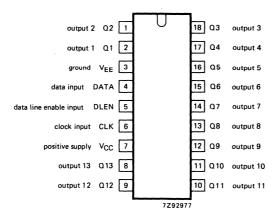

|                  | de Power S | Supplies (SMPS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |